Integrated 10/100 Fast Ethernet Transceiver

**Functional Specifications- Public**

Doc. No. MV-S103164-00,Rev. A

December 1, 2020

Document Classification: Proprietary Information

THIS DOCUMENT AND THE INFORMATION FURNISHED IN THIS DOCUMENT ARE PROVIDED "AS IS" WITHOUT ANY WARRANTY. MARVELL AND ITS AFFILIATES EXPRESSLY DISCLAIM AND MAKE NO WARRANTIES OR GUARANTEES, WHETHER EXPRESS, ORAL, IMPLIED, STATUTORY, ARISING BY OPERATION OF LAW, OR AS A RESULT OF USAGE OF TRADE, COURSE OF DEALING, OR COURSE OF PERFORMANCE, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NON-INFRINGEMENT.

This document, including any software or firmware referenced in this document, is owned by Marvell or Marvell's licensors, and is protected by intellectual property laws. No license, express or implied, to any Marvell intellectual property rights is granted by this document. The information furnished in this document is provided for reference purposes only for use with Marvell products. It is the user's own responsibility to design or build products with this information. Marvell products are not authorized for use as critical components in medical devices, military systems, life or critical support devices, or related systems. Marvell is not liable, in whole or in part, and the user will indemnify and hold Marvell harmless for any claim, damage, or other liability related to any such use of Marvell products.

Marvell assumes no responsibility for the consequences of use of such information or for any infringement of patents or other rights of third parties that may result from its use. You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning the Marvell products disclosed herein. Marvell and the Marvell logo are registered trademarks of Marvell or its affiliates. Please visit www.marvell.com for a complete list of Marvell trademarks and guidelines for use of such trademarks. Other names and brands may be claimed as the property of others.

Copyright © 2020. Marvell and/or its affiliates. All rights reserved.

#### **OVERVIEW**

The Marvell<sup>®</sup> 88E3016 device is the fourth generation Marvell<sup>®</sup> DSP-based physical layer transceiver for Fast Ethernet applications. The device contains all the active circuitry to convert data streams to and from a Media Access Controller (MAC) and the physical media. The 88E3016 device incorporates IEEE 802.3u Auto-Negotiation in support of both 100BASE-TX and 10BASE-T networks over twisted-pair cable in full-duplex or half-duplex mode.

The 88E3016 device supports the Reduced Gigabit Media Independent Interface (RGMII).

The 88E3016 device features a mode of operation supporting IEEE compliant 100BASE-FX fiber-optic networks. Additionally, the 88E3016 device implements Far-End Fault Indication (FEFI) in order to provide a mechanism for transferring information from the local station to the link partner that indicates a remote fault has occurred in 100BASE-FX mode.

The 88E3016 device features the Marvell Virtual Cable Tester<sup>®</sup> (VCT<sup>™</sup>) technology, which enables IT managers and networking equipment manufacturers to remotely analyze the quality and characteristics of the attached cable plant.

The 88E3016 device uses advanced mixed-signal processing and power management techniques for extremely low power dissipation and high port count system integration. The 88E3016 device is manufactured in an all CMOS process and packaged in a 64-pin QFN package.

#### **FEATURES**

- IEEE 802.3 compliant 100BASE-TX and 10BASE-T ports

- Reduced Gigabit Media Independent Interface (RGMII)

- Virtual Cable Tester<sup>®</sup> (VCT<sup>™</sup>) Technology

- PECL interface supporting 100BASE-FX applications

- Automatic MDI/MDIX crossover for 10BASE-T and 100BASE-TX

- Jumbo frame support to 10 Kbytes with up to ±150 ppm clock frequency difference

- IEEE 802.3u Auto-Negotiation support for automatic speed and duplex selection

- Far-End Fault Indication (FEFI) support for 100BASE-FX applications

- Supports 802.3ah Unidirectional Enable

- Energy detect feature

- Baseline wander correction

- Auto-Calibration for MAC Interface outputs

- COMA Mode support

- Flexible serial management interface (MDC/ MDIO) for register access

- Programmable interrupt to minimize polling

- IEEE 1149.1 Standard Test Access Port and boundary scan compatible

- Supports three (3) LEDs per port

- 0.15 μm standard digital CMOS process

- 64-pin QFN 9 mm x 9 mm package

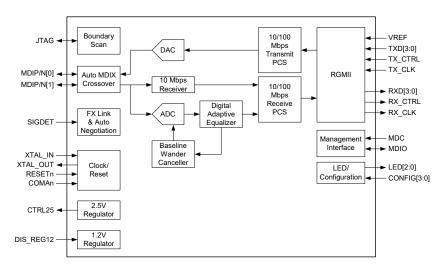

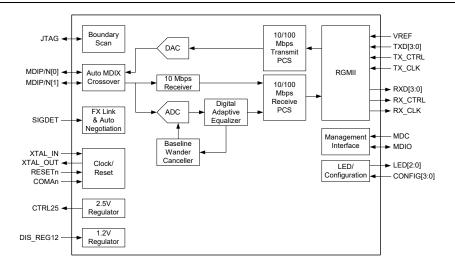

88E3016 Device Functional Block Diagram

# **Table of Contents**

| SEC  | TION 1. SIGNAL DESCRIPTION                                                                                                                                                                                       | . 8                              |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1.1  | 88E3016 Device 64-Pin QFN Pinout                                                                                                                                                                                 | . 8                              |

| 1.2  | Pin Description                                                                                                                                                                                                  | . 9                              |

| SEC  | TION 2. FUNCTIONAL DESCRIPTION1                                                                                                                                                                                  |                                  |

| 2.1  | Reduced Gigabit Media Independent Interface (RGMII)                                                                                                                                                              | 18                               |

| 2.2  | Serial Management Interface  2.2.1 MDC/MDIO Read and Write Operations  2.2.2 Preamble Suppression  2.2.3 Programming Interrupts                                                                                  | 19<br>20                         |

| 2.3  | Transmit and Receive Functions  2.3.1 Transmit Side Network Interface  2.3.2 Encoder  2.3.3 Receive Side Network Interface  2.3.4 Decoder  2.3.5 Auto-Negotiation                                                | 21<br>21<br>21<br>22             |

| 2.4  | Power Management                                                                                                                                                                                                 | 24<br>24<br>24                   |

| 2.5  | Regulators and Power Supplies         2.5.1       AVDD         2.5.2       AVDDC         2.5.3       AVDDR         2.5.4       AVDDX         2.5.5       DVDD         2.5.6       VDDO         2.5.7       VDDOR | 26<br>26<br>26<br>27<br>27<br>27 |

| 2.6  | Hardware Configuration                                                                                                                                                                                           | 28                               |

| 2.7  | Far End Fault Indication (FEFI)                                                                                                                                                                                  | 30                               |

| 2.8  | 802.3ah Unidirectional Enable                                                                                                                                                                                    | 30                               |

| 2.9  | Virtual Cable Tester® Feature                                                                                                                                                                                    | 31                               |

| 2.10 | Auto MDI/MDIX Crossover                                                                                                                                                                                          | 32                               |

| 2.11 | LED Interface                                         |          |

|------|-------------------------------------------------------|----------|

|      | 2.11.1 Manual Override                                |          |

|      | 2.11.2 PHY Control                                    |          |

|      | 2.11.3 LED Polarity                                   |          |

|      | 2.11.4 Stretching and Blinking                        | 38       |

| 2 12 | Automatic and Manual Impedance Calibration            | 30       |

| 2.12 | 2.12.1 MAC Interface Calibration Circuit              |          |

|      | 2.12.2 MAC Interface Calibration Register Definitions |          |

|      | 2.12.3 Changing Auto Calibration Targets              |          |

|      | 2.12.4 Manual Settings to The Calibration Registers   |          |

| 2.13 | CRC Error Counter                                     | 44       |

|      | 2.13.1 Enabling The CRC Error Counter                 | 44       |

| 2.14 | IEEE 1149.1 Controller                                | 45       |

|      | 2.14.1 Bypass Instruction                             | 45       |

|      | 2.14.2 Sample/Preload Instruction                     |          |

|      | 2.14.3 Extest Instruction                             |          |

|      | 2.14.4 The Clamp Instruction                          |          |

|      | 2.14.5 The HIGH-Z Instruction                         |          |

|      | 2.14.6 ID CODE Instruction                            | 47       |

| SEC  | CTION 3. REGISTER DESCRIPTION                         | 48       |

|      |                                                       |          |

| SEC  | CTION 4. ELECTRICAL SPECIFICATIONS                    | 78       |

| 4.1. | Absolute Maximum Ratings                              | 78       |

| 4.2. | Recommended Operating Conditions                      | 79       |

| 4.3  | Package Thermal Information                           | 80       |

|      | 4.3.1 88E3016 Device 64-Pin QFN package               |          |

| 4.4  | Current Consumption                                   | 81       |

|      | 4.4.1 Current Consumption AVDD + Center Tap           |          |

|      | 4.4.2 Current Consumption AVDDC                       |          |

|      | 4.4.3 Current Consumption DVDD                        |          |

|      | 4.4.4 Current Consumption VDDO + VDDOR                |          |

| 4.5. | DC Operating Conditions                               |          |

|      | 4.5.1 Non-RGMII Digital Pins                          |          |

|      | 4.5.2 Stub-Series Transceiver Logic (SSTL_2)          |          |

|      | 4.5.3 IEEE DC Transceiver Parameters                  | 86       |

| 4.6  | AC Electrical Specifications                          |          |

|      | •                                                     |          |

|      | 4.6.1 Reset and Configuration Timing                  | 87       |

|      | •                                                     | 87       |

| 4.7  | 4.6.1 Reset and Configuration Timing                  | 87<br>88 |

| 4.7  | 4.6.1 Reset and Configuration Timing                  | 87<br>88 |

| 4.8  | Latency Timing                                                        | 92        |

|------|-----------------------------------------------------------------------|-----------|

|      | 4.8.1 RGMII to 100BASE-TX Transmit Latency Timing                     | 92        |

|      | 4.8.2 RGMII to 10BASE-T Transmit Latency Timing                       | 92        |

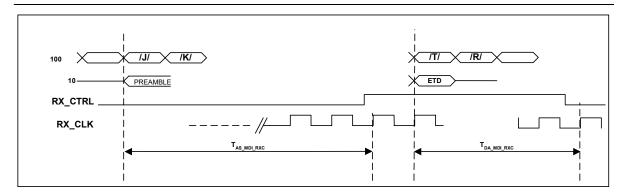

|      | 4.8.3 100BASE-TX to RGMII Receive Latency Timing                      | 93        |

|      | 4.8.4 10BASE-T to RGMII Receive Latency Timing                        | 93        |

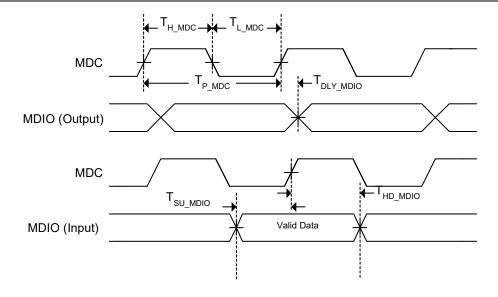

| 4.9  | Serial Management Timing                                              | 94        |

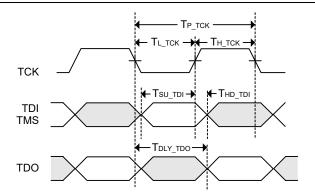

| 4.10 | JTAG Timing                                                           | 95        |

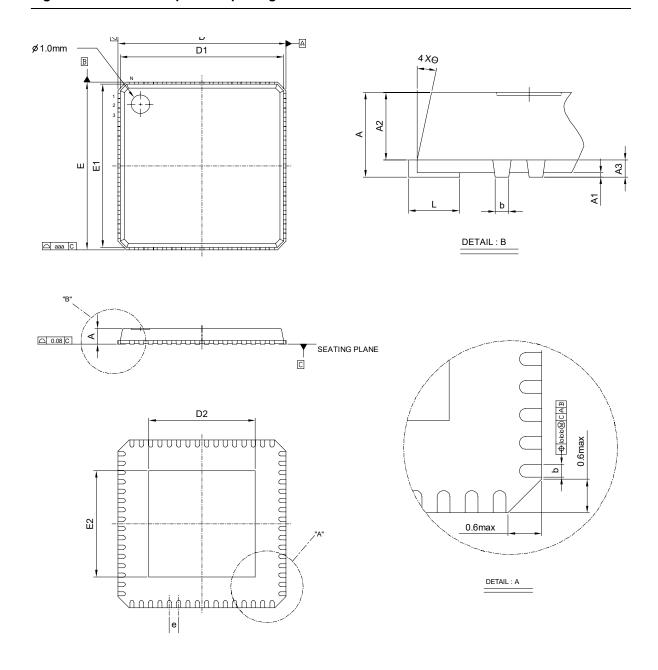

| SEC  | TION 5. PACKAGE MECHANICAL DIMENSIONS                                 | 96        |

| 5.1  | 88E3016 Package Mechanical Dimensions                                 | 96        |

| SEC  | TION 6. APPLICATION EXAMPLES                                          | 98        |

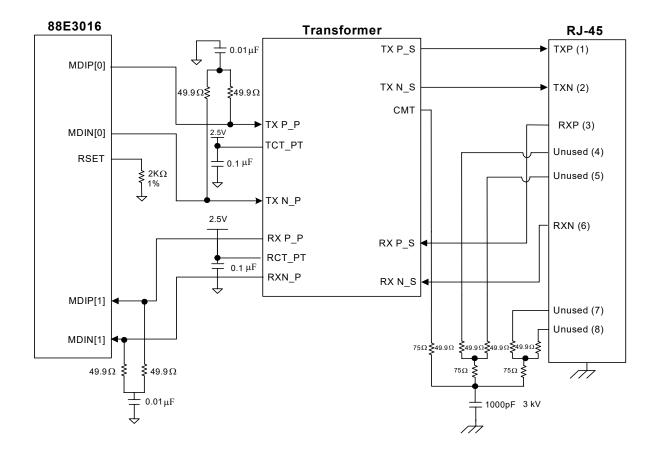

| 6.1  | 10BASE-T/100BASE-TX Circuit Application                               | 98        |

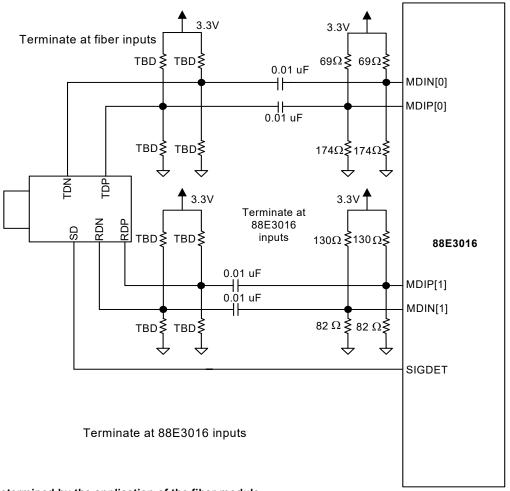

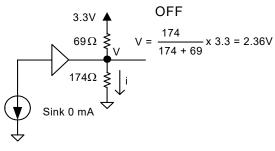

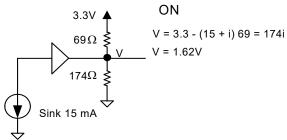

| 6.2  | FX Interface to 3.3V Fiber Transceiver                                | 99        |

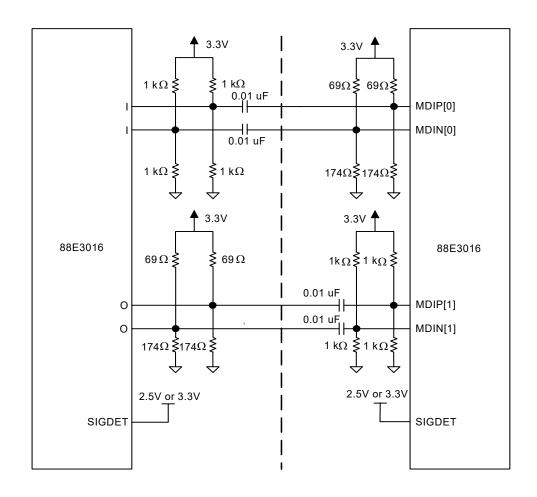

| 6.3  | Transmitter - Receiver Diagram                                        | 100       |

| 6.4  | 88E3016 to 88E3016 Backplane Connection - 100BASE-FX Interface        | 101       |

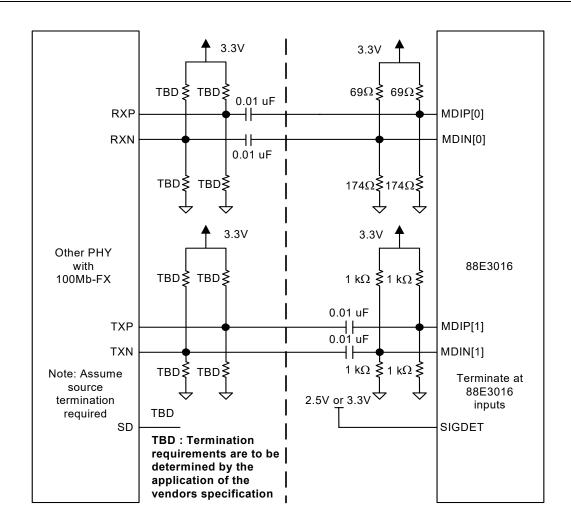

| 6.5  | 88E3016 to Another Vendor's PHY - 100BASE-FX Interface through a Back | kplane102 |

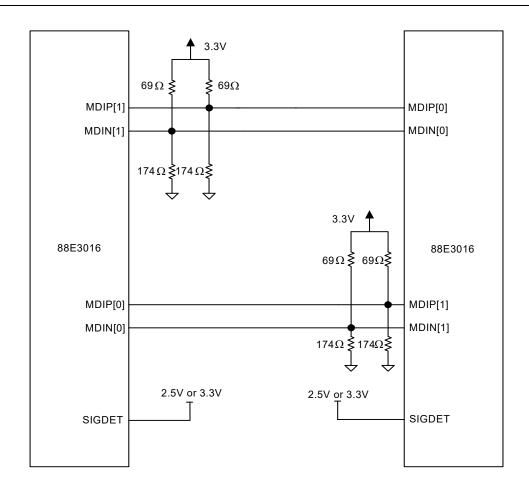

| 6.6  | Marvell® PHY to Marvell PHY Direct Connection                         | 103       |

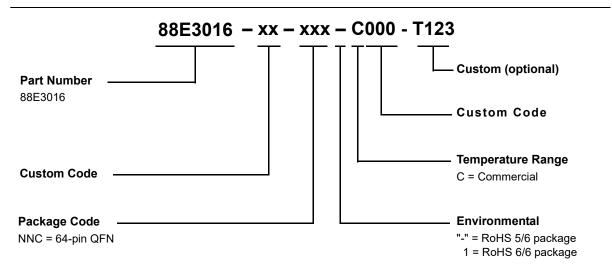

| SEC  | TION 7. ORDER INFORMATION                                             | 104       |

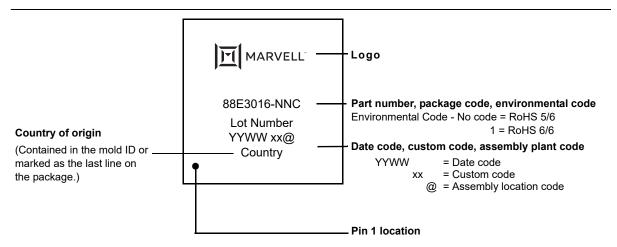

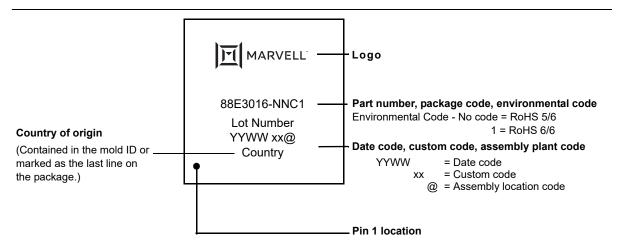

| 7.1  | Ordering Part Numbers and Package Markings                            | 104       |

# **Section 1. Signal Description**

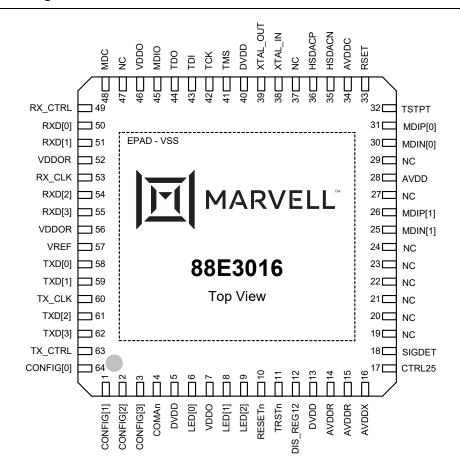

### 1.1 88E3016 Device 64-Pin QFN Pinout

The 88E3016 is manufactured in a 64-pin QFN.

Figure 1: 88E3016 Integrated 10BASE-T/100BASE-TX Fast Ethernet Transceiver 64-Pin QFN Package

# 1.2 Pin Description

# 1.2.1 Pin Type Definitions

| Pin Type | Definition            |  |

|----------|-----------------------|--|

| Н        | Input with hysteresis |  |

| I/O      | Input and output      |  |

| 1        | Input only            |  |

| 0        | Output only           |  |

| PU       | Internal pull up      |  |

| PD       | Internal pull down    |  |

| D        | Open drain output     |  |

| Z        | Tri-state output      |  |

| mA       | DC sink capability    |  |

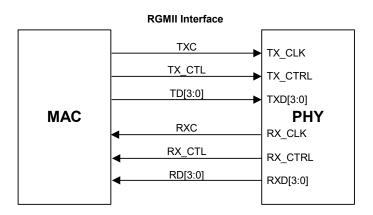

Table 1: RGMII Interface

| 88E3016        | Pin Name                                     | Type | Description                                                                                                                                                                              |

|----------------|----------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 60             | TX_CLK/TXC                                   | I    | RGMII Transmit Clock provides a 25 MHz or 2.5 MHz reference clock with ± 50 ppm tolerance depending on speed. In RGMII mode, TX_CLK is used as TXC.                                      |

| 63             | TX_CTRL/TX_CTL                               | I    | RGMII Transmit Control. TX_EN is presented on the rising edge of TX_CLK. In RGMII mode, TX_CTRL is used as TX_CTL.                                                                       |

|                |                                              |      | A logical derivative of TX_EN and TX_ER is presented on the falling edge of TX_CLK.                                                                                                      |

| 62<br>61<br>59 | TXD[3]/TD[3]<br>TXD[2]/TD[2]<br>TXD[1]/TD[1] | I    | RGMII Transmit Data. In RGMII mode, TXD[3:0] are used as TD[3:0].                                                                                                                        |

| 58             | TXD[0]/TD[0]                                 |      | The transmit data nibble is presented on TXD[3:0] on the rising edge of TX_CLK.                                                                                                          |

| 53             | RX_CLK/RXC                                   | 0    | RGMII Receive Clock provides a 25 MHz or 2.5 MHz reference clock with ± 50 ppm tolerance derived from the received data stream depending on speed. In RGMII mode, RX_CLK is used as RXC. |

| 49             | RX_CTRL/<br>RX_CTL                           | 0    | RGMII Receive Control. RX_DV is presented on the rising edge of RX_CLK. In RGMII mode, RX_CTRL is used as RX_CTL.                                                                        |

|                |                                              |      | A logical derivative of RX_DV and RX_ER is presented on the falling edge of RX_CLK.                                                                                                      |

| 55<br>54<br>51 | RXD[3]/RD[3]<br>RXD[2]/RD[2]<br>RXD[1]/RD[1] | 0    | RGMII Receive Data. In RGMII mode, RXD[3:0] are used as RD[3:0].                                                                                                                         |

| 50             | RXD[0]/RD[0]                                 |      | The receive data nibble is presented on RXD[3:0] on the rising edge of RX_CLK.                                                                                                           |

Table 2: Network Interface

| 88E3016  | Pin Name           | Type | Description                                                                                                                                                                                                 |

|----------|--------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31<br>30 | MDIP[0]<br>MDIN[0] | I/O  | Media Dependent Interface[0].  In MDI configuration, MDI[0]± is used for the transmit pair. In MDIX configuration, MDI[0]± is used for the receive pair.                                                    |

| 26<br>25 | MDIP[1]<br>MDIN[1] | I/O  | Media Dependent Interface[1].  In MDI configuration, MDI[1]± is used for the receive pair. In MDIX configuration, MDI[1]± is used for the transmit pair.                                                    |

| 18       | SIGDET             | I    | In 100BASE-FX mode, SIGDET indicates whether a signal is detected by the fiber optic transceiver. In 100BASE-TX/10BASE-T modes, this pin should not be left floating. It should be tied either high or low. |

Table 3: Serial Management Interface

| 88E3016 | Pin Name | Type | Description                                                                                                                                                                                                                          |

|---------|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 48      | MDC      | I    | MDC is the clock reference for the serial management interface. A continuous clock stream is not required (i.e., MDC can be stopped when the MDC/MDIO master is not sending a command). The maximum frequency supported is 8.33 MHz. |

| 45      | MDIO     | I/O  | MDIO is the management data. MDIO is used to transfer management data in and out of the device synchronously to MDC. This pin requires a pull-up resistor in a range from 1.5 kohm to 10 kohm.                                       |

Table 4: LED

| 88E3016 | Pin Name         | Type | Description                                                                                                                                                               |

|---------|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9       | LED[2]/Interrupt | 0    | Parallel LED outputs. See Section 2.11 "LED Interface" on page 33 for LED interface details. See Section 2.2.3 "Programming Interrupts" on page 20 for interrupt details. |

| 8       | LED[1]           | 0    | Parallel LED outputs. See Section 2.11 "LED Interface" on page 33 for LED interface details.                                                                              |

| 6       | LED[0]           | 0    | Parallel LED outputs. See Section 2.11 "LED Interface" on page 33 for LED interface details.                                                                              |

Table 5: JTAG

| 88E3016 | Pin Name | Type | Description                                                                                                                                                                                                                                                                                                                         |

|---------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 43      | TDI      | 1    | Boundary scan test data input. TDI contains an internal 150 kohm pull-up resistor.                                                                                                                                                                                                                                                  |

| 41      | TMS      | 1    | Boundary scan test mode select input. TMS contains an internal 150 kohm pull-up resistor.                                                                                                                                                                                                                                           |

| 42      | TCK      | 1    | Boundary scan test clock input. TCK contains an internal 150 kohm pull-up resistor.                                                                                                                                                                                                                                                 |

| 11      | TRSTn    | I    | Boundary scan test reset input. Active low. TRSTn contains an internal 150 kohm pull-up resistor as per the 1149.1 specification. After power up, the JTAG state machine should be reset by applying a low signal on this pin, or by keeping TMS high and applying 5 TCK pulses, or by pulling this pin low by a 4.7 kohm resistor. |

| 44      | TDO      | 0    | Boundary scan test data output.                                                                                                                                                                                                                                                                                                     |

Table 6: Clock/Configuration/Reset

| 88E3016           | Pin Name                                         | Type | Description                                                                                                                                                                                                                                             |

|-------------------|--------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

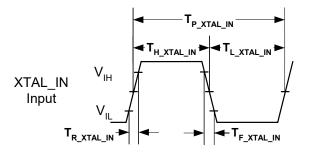

| 38                | XTAL_IN                                          | 1    | Reference Clock. 25 MHz ± 50 ppm tolerance crystal reference or oscillator input.                                                                                                                                                                       |

| 39                | XTAL_OUT                                         | 0    | Reference Clock. 25 MHz ± 50 ppm tolerance crystal reference. When the XTAL_OUT pin is not connected, it should be left floating. XTAL_OUT is used for crystal only. This pin should be left floating when an oscillator input is connected to XTAL_IN. |

| 3<br>2<br>1<br>64 | CONFIG[3]<br>CONFIG[2]<br>CONFIG[1]<br>CONFIG[0] | I    | Hardware Configuration. See "Hardware Configuration" on page 28.                                                                                                                                                                                        |

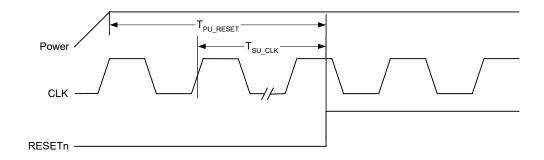

| 10                | RESETn                                           | I    | Hardware reset. Active low.  XTAL_IN/XTAL_OUT must be active for a minimum of 10 clock cycles before the rising edge of RESETn.  RESETn must be pulled high for normal operation.                                                                       |

| 57                | VREF                                             | 1    | RGMII input voltage reference.  Must be set to VDDOR/2 when used as 2.5V SSTL_2.  Set to VDDOR when used as 2.5V/3.3V LVCMOS.                                                                                                                           |

| 4                 | COMAn                                            | I    | COMA Control. Active low. If RESETn is low then COMAn has no effect. COMAn contains an internal 150 kohm pull-up resistor.  0 = In power saving mode 1 = Normal operation                                                                               |

Table 7: Regulator & Reference

| 88E3016 | Pin Name  | Type | Description                                                                                                                 |

|---------|-----------|------|-----------------------------------------------------------------------------------------------------------------------------|

| 33      | RSET      | I    | Constant voltage reference. External 2 kohm 1% resistor connection to VSS is required for this pin.                         |

| 12      | DIS_REG12 | 1    | 1.2V Regulator Disable. Tie to VDDO to disable, Tie to VSS to enable.                                                       |

| 17      | CTRL25    | 0    | 2.5V Regulator Control. This signal ties to the base of the BJT. If the 2.5V regulator is not used it can be left floating. |

Table 8: Test

| 88E3016 | Pin Name | Type | Description                                                                                                                                                                                                              |

|---------|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36      | HSDACP   | 0    | Test Pin. These pins have 49.9 ohm internal termination. They should be brought out to a via or pad to facilitate debug. If debug is not important and there are board space constraints, this pin can be left floating. |

| 35      | HSDACN   | 0    | Test Pin. These pins have 49.9 ohm internal termination. They should be brought out to a via or pad to facilitate debug. If debug is not important and there are board space constraints, this pin can be left floating. |

| 32      | TSTPT    | 0    | Test point. Leave unconnected.                                                                                                                                                                                           |

Table 9: **Power & Ground**

| 88E3016                                                  | Pin Name | Type   | Description                                                                                                                                                                                                                                                    |

|----------------------------------------------------------|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28                                                       | AVDD     | Power  | Analog supply. 2.5V <sup>1</sup> . AVDD can be supplied externally with 2.5V, or via the 2.5V regulator.                                                                                                                                                       |

| 34                                                       | AVDDC    | Power  | Analog supply - 2.5V or 3.3V <sup>2</sup> .  AVDDC must be supplied externally. Do not use the 2.5V regulator to power AVDDC.                                                                                                                                  |

| 14<br>15                                                 | AVDDR    | Power  | 1.2V Regulator supply - 2.5V AVDDR can be supplied externally with 2.5V, or via the 2.5V regulator. If the 1.2V regulator is not used, AVDDR must still be tied to 2.5V.                                                                                       |

| 16                                                       | AVDDX    | Power  | 2.5V Regulator supply - 3.3V.  AVDDX must be supplied externally. Note that this supply must be the same voltage as AVDDC.  If the 2.5V regulator is not used, then it means a 2.5V supply is in the system. AVDDX (along with AVDDC) should be left floating. |

| 5<br>13<br>40                                            | DVDD     |        | Digital core supply - 1.2V. DVDD can be supplied externally with 1.2V, or via the 1.2V regulator.                                                                                                                                                              |

| 7<br>46                                                  | VDDO     | Power  | 2.5V or 3.3V non-RGMII digital I/O supply <sup>3</sup> .  VDDO must be supplied externally. Do not use the 2.5V regulator to power VDDO.                                                                                                                       |

| 52<br>56                                                 | VDDOR    | Power  | 2.5V or 3.3V RGMII digital I/O supply <sup>4</sup> .  VDDOR must be supplied externally. Do not use the 2.5V regulator to power VDDOR.                                                                                                                         |

| EPAD                                                     | VSS      | Ground | Ground to digital core.  The 64-pin QFN package has an exposed die pad (E-PAD) at its base. This E-PAD must be soldered to VSS. Refer to the package mechanical drawings for the exact location and dimensions of the EPAD.                                    |

| 19<br>20<br>21<br>22<br>23<br>24<br>27<br>29<br>37<br>47 | NC       | NC     | No Connect. These pins are not bonded to the die and can be tied to anything.                                                                                                                                                                                  |

AVDD supplies the MDIP/N[1:0] pins.

AVDDC supplies the XTAL\_IN and XTAL\_OUT pins.

VDDO supplies the SIGDET, MDC, MDIO, RESETn, LED[2:0], CONFIG[3:0], TDI, TMS, TCK, TRSTn, TDO, COMAn, DIS\_REG12, CTRL25, HSDAC, and TSTPT pins.

<sup>4.</sup> VDDOR supplies the TXD[3:0], TX\_CLK, TX\_CTRL, RXD[3:0], RX\_CLK, and RX\_CTRL pins.

Table 10: I/O State at Various Test or Reset Modes

| Pin(s)                                                               | Isolate   | Loopback  | Software<br>Reset                        | Hardware<br>Reset | Power Down                               | Power<br>Down and<br>Isolate |

|----------------------------------------------------------------------|-----------|-----------|------------------------------------------|-------------------|------------------------------------------|------------------------------|

| MDIP/<br>N[1:0]                                                      | Active    | Active    | Tri-state                                | Tri-state         | Tri-state                                | Tri-state                    |

| TX_CLK                                                               | Tri-state | Active    | Active                                   | Tri-state         | Active                                   | Tri-state                    |

| RXD[0]<br>RXD[2]<br>RXD[3]<br>RXD[1]<br>RX_DV<br>RX_ER<br>CRS<br>COL | Tri-state | Active    | Low                                      | Low               | Low                                      | Tri-state                    |

| RX_CLK                                                               | Tri-state | Active    | Reg. 28.1 state<br>1 = Active<br>0 = Low | Low               | Reg. 28.1 state<br>1 = Active<br>0 = Low | Tri-state                    |

| MDIO                                                                 | Active    | Active    | Active                                   | Tri-state         | Active                                   | Active                       |

| LED                                                                  | Active    | Active    | Active                                   | High              | High                                     | High                         |

| TDO                                                                  | Tri-state | Tri-state | Tri-state                                | Tri-state         | Tri-state                                | Tri-state                    |

# 1.2.2 88E3016 64-Pin QFN Assignments - Alphabetical by Signal Name

| Pin # | Pin Name  | Pin # | Pin Name |

|-------|-----------|-------|----------|

| 28    | AVDD      | 29    | NC       |

| 34    | AVDDC     | 37    | NC       |

| 14    | AVDDR     | 47    | NC       |

| 15    | AVDDR     | 10    | RESETn   |

| 16    | AVDDX     | 33    | RSET     |

| 4     | COMAn     | 53    | RX_CLK   |

| 64    | CONFIG[0] | 49    | RX_CTRL  |

| 1     | CONFIG[1] | 50    | RXD[0]   |

| 2     | CONFIG[2] | 51    | RXD[1]   |

| 3     | CONFIG[3] | 54    | RXD[2]   |

| 17    | CTRL25    | 55    | RXD[3]   |

| 12    | DIS_REG12 | 18    | SIGDET   |

| 5     | DVDD      | 42    | тск      |

| 13    | DVDD      | 43    | TDI      |

| 40    | DVDD      | 44    | TDO      |

| 35    | HSDACN    | 41    | TMS      |

| 36    | HSDACP    | 11    | TRSTn    |

| 6     | LED[0]    | 32    | ТЅТРТ    |

| 8     | LED[1]    | 60    | TX_CLK   |

| 9     | LED[2]    | 63    | TX_CTRL  |

| 48    | MDC       | 58    | TXD[0]   |

| 30    | MDIN[0]   | 59    | TXD[1]   |

| 25    | MDIN[1]   | 61    | TXD[2]   |

| 45    | MDIO      | 62    | TXD[3]   |

| 31    | MDIP[0]   | 7     | VDDO     |

| 26    | MDIP[1]   | 46    | VDDO     |

| 19    | NC        | 52    | VDDOR    |

| 20    | NC        | 56    | VDDOR    |

| 21    | NC        | 57    | VREF     |

| 22    | NC        | EPAD  | VSS      |

| 23    | NC        | 38    | XTAL_IN  |

| 24    | NC        | 39    | XTAL_OUT |

| 27    | NC        |       |          |

# **Section 2. Functional Description**

Figure 2 shows the functional block for the 88E3016 device. The transmitter and transmit PCS block are fully described on page 21. The receiver and receive PCS block are fully described on page 21.

Figure 2: 88E3016 Device Functional Block Diagram

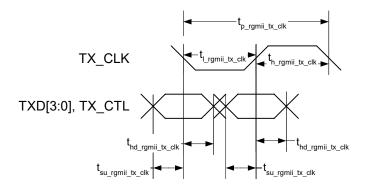

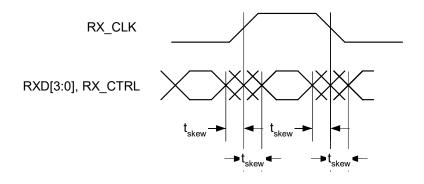

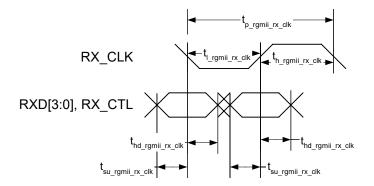

# 2.1 Reduced Gigabit Media Independent Interface (RGMII)

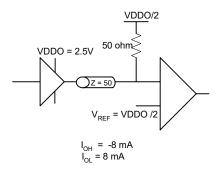

The 88E3016 device supports the RGMII specification (Version 1.2a, 9/22/2000, version 2.0, 04/2002 - except instead of HSTL, it supports 2.5V SSTL\_2).

Figure 3: RGMII Signal Diagram

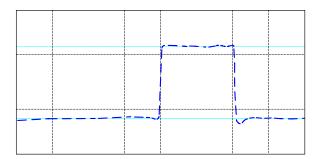

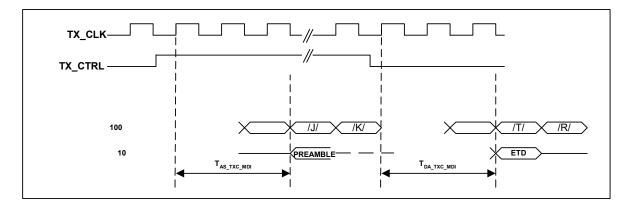

The interface runs at 2.5 MHz for 10 Mbps and 25 MHz for 100 Mbps. The TX\_CLK signal is always generated by the MAC, and the RX\_CLK signal is generated by the PHY.

During packet reception, RX\_CLK may be stretched on either the positive or negative pulse to accommodate the transition from the free running clock to a data synchronous clock domain. When the speed of the PHY changes, a similar stretching of the positive or negative pulse is allowed. No glitching of the clocks is allowed during speed transitions.

The MAC must hold TX\_CTRL low until the MAC has ensured that TX\_CTRL is operating at the same speed as the PHY.

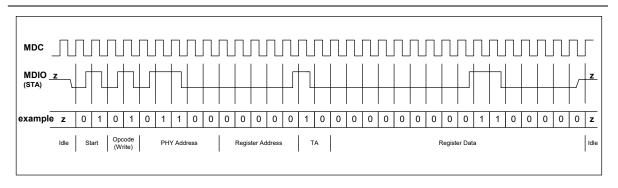

# 2.2 Serial Management Interface

The serial management interface provides access to the internal registers via the MDC and MDIO pins and is compliant to IEEE 802.3u section 22. MDC is the management data clock input and can run from DC to a maximum rate of 8.33 MHz. MDIO is the management data input/output and is a bi-directional signal that runs synchronously to MDC. The MDIO pin requires a 1.5 kohm pull-up resistor that pulls the MDIO high during idle and turnaround times.

### 2.2.1 MDC/MDIO Read and Write Operations

All the relevant serial management registers are implemented as well as several optional registers. A description of the registers can be found in Section 3. "Register Description" on page 48.

MDIO Z MDIO (PHY) 0 0 0 0 0 0 0 0 0 0 0 PHY Address Start Register Data

Figure 4: Typical MDC/MDIO Read Operation

Table 11 is an example of a read operation.

Table 11: Serial Management Interface Protocol

| 32-Bit<br>Pream |    | Start of<br>Frame | Opcode<br>Read = 10<br>Write = 01 | 5-Bit Phy<br>Device<br>Address | 5-Bit Phy<br>Register<br>Address | 2-Bit<br>Turn-<br>around<br>Read = z0<br>Write = 10 | 16-Bit Data Field | Idle     |

|-----------------|----|-------------------|-----------------------------------|--------------------------------|----------------------------------|-----------------------------------------------------|-------------------|----------|

| 111111          | 11 | 01                | 10                                | 01100                          | 00000                            | z0                                                  | 0001001100000000  | 11111111 |

## 2.2.2 Preamble Suppression

The 88E3016 devices are permanently programmed for preamble suppression. A minimum of one idle bit is required between operations.

## 2.2.3 Programming Interrupts

When Register 22:11:8 is set to 1110, the interrupt functionality is mapped to the LED[2] pin. The interrupt function drives the LED[2] pin active whenever an interrupt event is enabled by programming register 18. The polarity of the interrupt signal is determined by Register 25.14. This function minimizes the need for polling via the serial management interface. Table 12 shows the interrupts that may be programmed.

Table 12: Programmable Interrupts

| Register<br>Address | Programmable Interrupts                     |

|---------------------|---------------------------------------------|

| 18.14               | Speed Changed Interrupt Enable              |

| 18.13               | Duplex Changed Interrupt Enable             |

| 18.12               | Page Received Interrupt Enable              |

| 18.11               | Auto-Negotiation Completed Interrupt Enable |

| 18.10               | Link Status Changed Interrupt Enable        |

| 18.9                | Symbol Error Interrupt Enable               |

| 18.8                | False Carrier Interrupt Enable              |

| 18.7                | FIFO Over/Underflow Interrupt Enable        |

| 18.6                | MDI/MDIX Crossover Changed Enable           |

| 18.4                | Energy Detect Changed Enable                |

| 18.1                | Polarity Changed Enable                     |

| 18.0                | Jabber Interrupt Enable                     |

Register 18 determines whether the LED[2] pin is asserted when an interrupt event occurs. Register 19 reports interrupt status. When an interrupt event occurs, the corresponding bit in register 19 is set and remains set until register 19 is read via the serial management interface. When interrupt enable bits are not set in register 18, interrupt status bits in register 19 are still set when the corresponding interrupt events occur. However, the LED[2] pin is not asserted.

The LED[2] pin is active as long as at least one interrupt status bit is set in register 19 with its corresponding interrupt enable bit set in register 18, and Register 22:11:8 = 1110.

To de-assert the LED[2] pin:

- Clear of register 19 via a serial management read

- Disable the interrupt enable by writing register 18

### 2.3 Transmit and Receive Functions

The transmit and receive paths for the 88E3016 device are described in the following sections.

#### 2.3.1 Transmit Side Network Interface

#### 2.3.1.1 Multi-mode TX Digital to Analog Converter

The 88E3016 device incorporates a multi-mode transmit DAC to generate filtered MLT-3, NRZI, or Manchester coded symbols. The transmit DAC performs signal wave shaping to reduce EMI. The transmit DAC is designed for very low parasitic loading capacitances to improve the return loss requirement, which allows the use of low cost transformers.

#### 2.3.1.2 Slew Rate Control and Waveshaping

In 100BASE-TX mode, slew rate control is used to minimize high frequency EMI. In 10BASE-T mode, the output waveform is pre-equalized via a digital filter.

#### 2.3.2 Encoder

#### 2.3.2.1 100BASE-TX

In 100BASE-TX mode, the transmit data stream is 4B/5B encoded, serialized, and scrambled. Upon initialization, the initial scrambling seed is determined by the PHY address. The datastream is then MLT-3 coded.

#### 2.3.2.2 10BASE-T

In 10BASE-T mode, the transmit data is serialized and converted to Manchester encoding.

#### 2.3.2.3 100BASE-FX

In 100BASE-FX mode, the transmit data stream is 4B/5B encoded, serialized, and converted to NRZI.

#### 2.3.3 Receive Side Network Interface

#### 2.3.3.1 Analog to Digital Converter

The 88E3016 device incorporates an advanced high speed ADC on each receive channel with greater resolution for better SNR, and therefore, lower error rates. Patented architectures and design techniques result in high differential and integral linearity, high power supply noise rejection, and low metastability error rate.

#### 2.3.3.2 Baseline Wander Canceller

The 88E3016 device employs an advanced baseline wander cancellation circuit to automatically compensate for this DC shift. It minimizes the effect of DC baseline shift on the overall error rate.

#### 2.3.3.3 Digital Adaptive Equalizer

The digital adaptive equalizer removes inter-symbol interference at the receiver. The digital adaptive equalizer takes unequalized signals from ADC output and uses a combination of feedforward equalizer (FFE) and decision feedback equalizer (DFE) for the best-optimized signal-to-noise (SNR) ratio.

#### 2.3.3.4 Link Monitor

The link monitor is responsible for determining if link is established with a link partner. In 10BASE-T mode, link monitor function is performed by detecting the presence of valid link pulses (NLPs) on the MDI± pins.

In 100BASE-TX mode, link is established by scrambled idles.

See Section 2.8 for unidirectional enable.

#### 2.3.3.5 Copper Signal Detection

In 100BASE-TX mode, the signal detection function is based on the receive signal energy detected on the MDI± pins that is continuously qualified by the squelch detect circuit, and the local receiver acquiring lock.

#### 2.3.3.6 Fiber Signal Detection

The SIGDET pin is used to qualify whether there is receive energy on the line. Register 16.6 determines the polarity of the SIGDET pin. When Register 16.6 is set low, the SIGDET pin polarity is active high, otherwise the polarity is active low.

#### 2.3.4 Decoder

#### 2.3.4.1 100BASE-TX

In 100BASE-TX mode, the receive data stream is recovered and converted to NRZ. The NRZ stream is descrambled and aligned to the symbol boundaries. The aligned data is then parallelized and 5B/4B decoded. The receiver does not attempt to decode the data stream unless the scrambler is locked. The descrambler "locks" to the *scrambler* state after detecting a sufficient number of consecutive idle code-groups. Once locked, the descrambler continuously monitors the data stream to make sure that it has not lost synchronization. The descrambler is always forced into the *unlocked* state when a link failure condition is detected, or when insufficient idle symbols are detected.

#### 2.3.4.2 10BASE-T

In 10BASE-T mode, the recovered 10BASE-T signal is decoded from Manchester to NRZ, and then aligned. The alignment is necessary to insure that the start of frame delimiter (SFD) is aligned to the nibble boundary.

#### 2.3.4.3 100BASE-FX

In 100BASE-FX mode the receive data stream is received and converted to NRZ. The decoding process is identical to 100BASE-TX except no descrambling is necessary.

### 2.3.5 Auto-Negotiation

The 88E3016 device can auto-negotiate to operate in 10BASE-T or 100BASE-TX

If Auto-Negotiation is enabled, then the 88E3016 devices negotiate with the link partner to determine the speed and duplex with which to operate. If the link partner is unable to Auto-Negotiate, the 88E3016 devices go into the parallel detect mode to determine the speed of the link partner. Under parallel detect mode, the duplex mode is fixed at half-duplex.

#### 2.3.5.1 Register Update

Auto-Negotiation is initiated upon any of the following conditions:

- Power up reset

- Hardware reset

- Software reset

- Restart Auto-Negotiation

- Transition from power down to power up

- · Changing from the link-up state to the linkfail state

Changes to the AnegEn, SpeedLSB, and Duplex bits (Registers 0.12, 0.13, and 0.8, respectively) do not take effect unless one of the following takes place:

- Software reset (SWReset bit Register 0.15)

- Restart Auto-Negotiation (RestartAneg bit Register 0.9)

- Transition from power down to power up (PwrDwn bit Register 0.11)

- The link goes down

The Auto-Negotiation Advertisement register (Register 4) is internally latched once every time Auto-Negotiation enters the *ability detect* state in the arbitration state machine. Hence, a write into the Auto-Negotiation Advertisment Register has no effect once the 88E3016 devices begin to transmit Fast Link Pulses (FLPs). This guarantees that a sequence of FLPs transmitted is consistent with one another.

The Next Page Transmit register (Register 7) is internally latched once every time Auto-Negotiation enters the next page exchange state in the arbitration state machine.

### 2.3.5.2 Next Page Support

The 88E3016 devices support the use of next page during Auto-Negotiation. By default, the received base page and next page are stored in the Link Partner Ability register - Base Page (Register 5). The 88E3016 devices have an option to write the received next page into the Link Partner Next Page register - Register 8 - (similar to the description provided in the IEEE 802.3ab standard) by programming the Reg8NxtPg bit (PHY Specific Control Register - Register 16.12).

# 2.4 Power Management

The 88E3016 devices support advanced power management modes that conserve power.

Three low power modes are supported in the 88E3016 devices.

- IEEE 802.3 22.2.4.1.5 compliant power down

- Energy Detect+<sup>TM</sup>

- COMA mode

IEEE 22.2.4.1.5 power down compliance allows for the PHY to be placed in a low-power consumption state by register control.

Energy Detect+<sup>TM</sup> allows the 88E3016 devices to wake up when energy is detected on the wire with the additional capability to wake up a link partner. The 10BASE-T link pulses are sent once every second while listening for energy on the line.

COMA mode shuts down the PHY into a low power state.

Table 13 displays the low power operating mode selection.

Table 13: Operating Mode Selection

| Power Mode                   | How to Activate Mode                                            |

|------------------------------|-----------------------------------------------------------------|

| IEEE Power Down              | PwrDwn bit write (Register 0.11)                                |

| Energy Detect+ <sup>TM</sup> | Configuration option & register EDet bit write (Register 16.14) |

| COMA                         | COMAn pin                                                       |

#### 2.4.1 IEEE Power Down Mode

The standard IEEE power down mode is entered by setting Register 0.11 equal to one. In this mode, the PHY does not respond to any MAC interface signals except the MDC/MDIO. It also does not respond to any activity on the CAT 5 cable.

In this power down mode, the PHY cannot wake up on its own by detecting activity on the CAT 5 cable. It can only wake up by clearing the PwrDwn bit to 0.

# 2.4.2 Energy Detect +TM

When Register 16.14 is enabled, the Energy Detect +™ mode is enabled. In this mode, the PHY sends out a single 10 Mbps NLP (Normal Link Pulse) every one second. If the 88E3016 devices are in Energy Detect+ mode, it can wake a connected device. The 88E3016 devices also respond to MDC/MDIO.

# 2.4.3 Normal 10/100 Mbps Operation

Normal 10/100 Mbps operation can be entered by either using a configuration option or a register write during the energy detect mode.

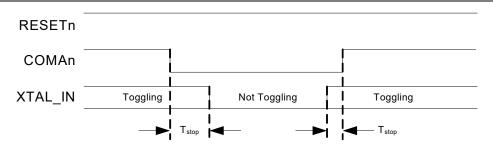

#### 2.4.4 COMA Mode

COMA mode shuts down the PHY into a low power state when it is not being used. When the PHY is in the COMA mode, the PHY is completely non-functional including register access. COMA mode is entered when the COMAn pin is set low.

If hardware reset pin (RESETn) and the COMA pin (COMAn) are asserted simultaneously the hardware reset function has priority over the COMA function.

If the PHY is disabled by removing any one or more of the external power supplies then the COMAn pin has no functionality. If the PHY is re-enabled then the proper power up sequence must be followed and a hardware reset applied before the PHY enters into the normal operating state.

If the reference clock (XTAL\_IN, XTAL\_OUT) stops when the PHY is disabled then the reference clock must be restarted and hardware reset must be applied before the PHY enters into the normal operating state.

If all external power supplies remain powered up and the reference clock continues to run then the PHY can enter and exit the COMA state without the need for hardware reset by simply controlling the COMAn pin. If XTAL\_IN is attached to an oscillator instead of a crystal and if the reference clock can be cleanly switched between toggling at 25 MHz and non-toggling state without glitches then the XTAL\_IN can be stopped if the relationship shown in Figure 6 can be met. Tstop should be at least 1 ms. Tstart should be at least 0 ms.

Note that if the power supply and reference clock requirements can be met then all registers will retain their values during the COMA state.

Figure 6: XTAL IN to COMAn Relationship

#### **Regulators and Power Supplies** 2.5

The 88E3016 device can operate from a single 2.5V or 3.3V supply if the regulators are used. If regulators are not used then a 2.5V and 1.2V supply are needed. Table 14 lists the valid combinations of regulator usage.

The VDDO supply can run at 2.5V or 3.3V and that the VDDOR supply can run at 2.5V or 3.3V. The 2.5V generated by the 2.5V regulator must not be used to supply VDDO or VDDOR.

The AVDDC and AVDDX must always be at the same voltage level, if AVDDX is not floating.

Table 14: **Power Supply Options**

| Supply                      | Pin Name                                             | AVDDC                     | AVDDX             | AVDD             | AVDDR             | DVDD                               |

|-----------------------------|------------------------------------------------------|---------------------------|-------------------|------------------|-------------------|------------------------------------|

| Configuration<br>Option     | Comment                                              | High<br>Voltage<br>Analog | 2.5V<br>Regulator | 2.5V<br>Analog   | 1.2V<br>Regulator | 1.2V Digital                       |

| Single 3.3V supply          | Need External BJT<br>DIS_REG12 = VSS                 | 3.3V<br>External          | 3.3V<br>External  | 2.5V<br>from BJT | 2.5V<br>from BJT  | 1.2V from<br>Internal<br>Regulator |

| 3.3V supply and 1.2V supply | Need External BJT<br>DIS_REG12 = VDDO                | 3.3V<br>External          | 3.3V<br>External  | 2.5V<br>from BJT | 2.5V<br>from BJT  | 1.2V<br>External                   |

| Single 2.5V supply          | Do not connect exter-<br>nal BJT<br>DIS_REG12 = VSS  | 2.5V External             | Floating          | 2.5V<br>External | 2.5V<br>External  | 1.2V from<br>Internal<br>Regulator |

| 2.5V supply and 1.2V supply | Do not connect exter-<br>nal BJT<br>DIS_REG12 = VDDO | 2.5V External             | Floating          | 2.5V<br>External | 2.5V<br>External  | 1.2V<br>External                   |

The 2.5V regulator is not used if CTRL25 is left floating and not connected to a BJT.

The 1.2V regulator is disabled when DIS\_REG12 is tied to VDDO. It is enabled when DIS\_REG12 is tied to VSS.

#### 2.5.1 AVDD

AVDD is used as the 2.5V analog supply. AVDD can be supplied externally with 2.5V, or via the 2.5V regulator.

#### 2.5.2 AVDDC

AVDDC is used as the high voltage analog supply and can run on 2.5V or 3.3V.

AVDDC must be supplied externally. Do not use the 2.5V regulator to power AVDDC.

#### 2.5.3 **AVDDR**

AVDDR is used as the 2.5V supply to the internal regulator that generates the 1.2V digital supply.

AVDDR can be supplied externally with 2.5V, or via the 2.5V regulator.

If the 1.2V regulator is not used, AVDDR must still be tied to 2.5V.

#### 2.5.4 AVDDX

AVDDX is used as the 3.3V supply to the external regulator that generates the 2.5V supply.

If the 2.5V regulator is not used, then the CTRL25 pin should be left floating. In this particular case when the 2.5V regulator is not used, the AVDDX should be left floating.

AVDDX must be supplied externally. Note that this supply must be the same voltage as AVDDC.

#### 2.5.5 **DVDD**

DVDD is used as the 1.2V digital supply.

DVDD can be supplied externally with 1.2V, or via the 1.2V regulator.

All DVDD pins should be shorted together. A decoupling capacitor should be attached to pin 13 of the 88E3016 device.

#### 2.5.6 VDDO

VDDO supplies the non-RGMII digital I/O pins. The voltage range is 2.5V or 3.3V.

VDDO must be supplied externally. Do not use the 2.5V regulator to power VDDO.

#### 2.5.7 **VDDOR**

VDDOR supplies the RGMII digital I/O pins. The voltage should be 2.5V or 3.3V.

VDDOR must be supplied externally. Do not use the 2.5V regulator to power VDDOR.

Three options are supported:

- 2.5V LVCMOS

- 3.3V LVCMOS

- 2.5V SSTL 2

The VREF pin should be set to 0.5 x VDDOR for SSTL\_2 behavior.

The VREF pin should be tied to VDDOR for LVCMOS behavior.

Note that 3.3V SSTL\_2 is not supported.

# 2.6 Hardware Configuration

The 88E3016 device is configured by tying LED[1:0], VDDO, or VSS to CONFIG[3:0]. After the deassertion of RESET the 88E3016 will be hardware configured. The CONFIG pins should not be left floating.

The LED, CRS, and COL outputs a bit stream during initialization that is used by the CONFIG pin inputs. The bit values are latched at the deassertion of hardware reset. The bit stream mapping for 88E3016 is shown in Table 15.

Table 15: 88E3016 Three bit Mapping

| Pin    | Bits 2,1,0 |

|--------|------------|

| VSS    | 000        |

| LED[0] | 001        |

| LED[1] | 010        |

| VDDO   | 111        |

The 3 bits for each CONFIG pin are mapped as shown in Table 16.

**Table 16: Configuration Mapping**

| Pin       | Bit 2    | Bit 1    | Bit 0    |

|-----------|----------|----------|----------|

| CONFIG[0] | Reserved | PHYAD[1] | PHYAD[0] |

| CONFIG[1] | Reserved | PHYAD[3] | PHYAD[2] |

| CONFIG[2] | Reserved | ENA_XC   | PHYAD[4] |

| CONFIG[3] | MODE[2]  | MODE[1]  | MODE[0]  |

Each bit in the configuration is defined as shown in Table 17.

Table 17: 88E3016 Configuration Definition

| Bits       | Definition                                                           | Bits Affected                                |  |

|------------|----------------------------------------------------------------------|----------------------------------------------|--|

| PHYAD[4:0] | PHY Address                                                          | None                                         |  |

| ENA_XC     | 0 = Default Disable Auto-Crossover                                   | 16.5:4                                       |  |

|            | 1 = Default Enable Auto-Crossover                                    | In 100BASE-FX mode, this should be disabled. |  |

| MODE[2:0]  | 000 = Copper - RGMII, Receive clock transition when data transitions | 28.11:10, 28.3                               |  |

|            | 001 = Copper - RGMII, Receive clock transition when data stable      |                                              |  |

|            | 010 = Fiber - RGMII, Receive clock transition when data transitions  |                                              |  |

|            | 111 = Fiber - RGMII, Receive clock transition when data stable       |                                              |  |

Table 18 clarifies how the MODE[2:0] affects the register defaults.

Table 18: MODE[2:0] to Register Default Mapping

| MODE[2:0]              | MAC Interface<br>Mode | Fiber/Copper |

|------------------------|-----------------------|--------------|

|                        | 28.11:10              | 28.3         |

| 000 (CONFIG3 = VSS)    | 00                    | 0            |

| 001 (CONFIG3 = LED[0]) | 01                    | 0            |

| 010 (CONFIG3 = LED[1]) | 00                    | 1            |

| 011 (CONFIG3 = LED[2]) | 10                    | 0            |

| 111 (CONFIG3 = VDDO)   | 01                    | 1            |

# 2.7 Far End Fault Indication (FEFI)

Far end fault indication provides a mechanism for transferring information from the local station to the link partner that a remote fault has occurred in 100BASE-FX mode.

A remote fault is an error in the link that one station can detect while the other one cannot. An example of this is a disconnected wire at a station's transmitter. This station is receiving valid data and detects that the link is good via the link monitor, but is not able to detect that its transmission is not propagating to the other station.

A 100BASE-FX station that detects this remote fault modifies its transmitted idle stream pattern from all ones to a group of 84 ones followed by one zero. This is referred to as the FEFI idle pattern.

The FEFI function is controlled by the FEFI bits in 100BASE-FX mode.

Register 16.8 enables and disables the FEFI function. This bit has no effect in 10BASE-T and 100BASE-TX modes.

### 2.8 802.3ah Unidirectional Enable

The 88E3016 devices support the 802.3ah Unidirectional Enable function. When this function is enabled the PHY transmit path is enabled even if there is no link established. To enable unidirectional transmitting, all the following conditions must be met. Unidirectional is enabled (0.5 = 1). Auto-Negotiation is disabled (0.12 = 0). Full duplex enabled (0.8 = 1). Register 1.7 indicates that the PHY is able to transmit from the media independent interface regardless of whether the PHY has determined that a valid link has been established.

# 2.9 Virtual Cable Tester® Feature

The 88E3016 devices Virtual Cable Tester (VCT™) feature uses Time Domain Reflectometry (TDR) to determine the quality of the cables, connectors, and terminations. Some of the possible problems that can be diagnosed include opens, shorts, cable impedance mismatch, bad connectors, termination mismatch, and bad magnetics.

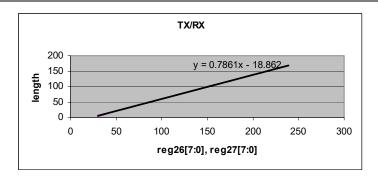

The 88E3016 devices transmit a signal of known amplitude (+1V) down each of the two pairs of an attached cable. It will conduct the cable diagnostic test on each pair, testing the TX and RX pairs sequentially. The transmitted signal will continue down the cable until it reflects off of a cable imperfection. The magnitude of the reflection and the time it takes for the reflection to come back are shown in the VCT registers 26.12:8, 26.7:0, 27.12:8, and 27.7:0 respectively.

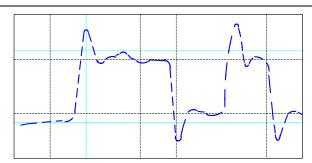

Using the information from the VCT Registers 26 and 27, the distance to the problem location and the type of problem can be determined. For example, the time it takes for the reflection to come back, can be converted to distance using the cable fault distance trend line tables in Figure 7. The polarity and magnitude of the reflection together with the distance will indicate the type of discontinuity. For example, a +1V reflection will indicate an open close to the PHY and a -1V reflection will indicate a short close to the PHY.

When the cable diagnostic feature is activated by setting Register 26.15 bit to one, a pre-determined amount of time elapses before a test pulse is transmitted. This is to ensure that the link partner loses link, so that it stops sending 100BASE-TX idles or 10 Mbit data packets. This is necessary to be able to perform the TDR test. The TDR test can be performed either when there is no link partner or when the link partner is Auto-Negotiating or sending 10 Mbit idle link pulses. If the 88E3016 devices receive a continuous signal for 125 ms, it will declare test failure because it cannot start the TDR test. In the test fail case, the received data is not valid. The results of the test are also summarized in Register 26.14:13 and 27.14:13.

- 11 = Test fail (The TDR test could not be run for reasons explained above)

- 00 = Valid test, normal cable (no short or open in cable)

- 10 = Valid test, open in cable (Impedance > 333 ohms)

- 01 = Valid test, short in cable (Impedance < 33 ohms)</li>

The definition for shorts and opens is arbitrary and the user can define it anyway they desire using the information in the VCT registers. The impedance mismatch at the location of the discontinuity could also be calculated knowing the magnitude of the reflection. Refer to the App Note "Virtual Cable Tester® -- How to use TDR results" for details.

Figure 7: Cable Fault Distance Trend Line

### 2.10 Auto MDI/MDIX Crossover

The 88E3016 devices automatically determine whether or not it needs to cross over between pairs so that an external crossover cable is not required. If the 88E3016 devices interoperate with a device that cannot automatically correct for crossover, the 88E3016 devices make the necessary adjustment prior to commencing Auto-Negotiation. If the 88E3016 devices interoperate with a device that implements MDI/MDIX crossover, a random algorithm as described in IEEE 802.3 section 40.4.4 determines which device performs the crossover.

When the 88E3016 devices interoperate with legacy 10BASE-T devices that do not implement Auto-Negotiation, the 88E3016 devices follow the same algorithm as described above since link pulses are present. However, when interoperating with legacy 100BASE-TX devices that do not implement Auto-Negotiation (i.e. link pulses are not present), the 88E3016 devices use signal detect to determine whether or not to crossover.

The Auto MDI/MDIX crossover function can be disabled via Register 16.5:4.

The 88E3016 devices are set to MDI mode by default if auto MDI/MDIX crossover is disabled at hardware reset.

The pin mapping in MDI and MDIX modes is specified in Table 19. Refer to Figure 24 on page 98 for magnetics details.

Table 19: **MDI/MDIX Pin Functions**

| Physical Pin | M                   | DIX      | М          | DI       |

|--------------|---------------------|----------|------------|----------|

|              | 100BASE-TX 10BASE-T |          | 100BASE-TX | 10BASE-T |

| MDIP/N[1]    | Transmit            | Transmit | Receive    | Receive  |

| MDIP/N[0]    | Receive             | Receive  | Transmit   | Transmit |

### 2.11 LED Interface

The LEDs can either be controlled by the PHY or controlled externally, independent of the state of the PHY.

#### 2.11.1 Manual Override

External control is achieved by writing to the PHY Manual LED Override register 25.5:0. Any of the LEDs can be turned on, off, or made to blink at variable rates independent of the state of the PHY. This independence eliminates the need for driving LEDs from the MAC or the CPU. If the LEDs are driven from the CPU located at the back of the board, the LED lines crossing the entire board will pick up noise. This noise will cause EMI issues. Also, PCB layout will be more difficult due to the additional lines routed across the board.

When the LEDs are controlled by the PHY, the activity of the LEDs is determined by the state of the PHY. Each LED can be programmed to indicate various PHY states, with variable blink rate.

Any one of the LEDs can be controlled independently of the other LEDs (i.e one LED can be externally controlled while another LED can be controlled by the state of the PHY).

Table 20: Manual Override

| Bits   | Field     | Description   |

|--------|-----------|---------------|

| 25.5:4 | ForceLED2 | 00 = Normal   |

|        |           | 01 = Blink[1] |

|        |           | 10 = LED Off  |

|        |           | 11 = LED On   |

| 25.3:2 | ForceLED1 | 00 = Normal   |

|        |           | 01 = Blink    |

|        |           | 10 = LED Off  |

|        |           | 11 = LED On   |

| 25.1:0 | ForceLED0 | 00 = Normal   |

|        |           | 01 = Blink    |

|        |           | 10 = LED Off  |

|        |           | 11 = LED On   |

### 2.11.2 PHY Control

Manual override is disabled (25.5:4, 25.3:2, 25.1:0 is set to 00) then the LED behavior is defined by register 22.11:8, 22.7:4, and 22.3:0 (Table 21). If SPEED is selected then the LED behavior is further qualified by register 24.8:6, 24.5:3, and 24.2:0 (Table 22). See 2.2.3 "Programming Interrupts" when 22.11:8 is set to 1110.

Table 21: PHY LED Control

| Bits    | Field | Description                             |

|---------|-------|-----------------------------------------|

| 22.11:8 | LED2  | LED2 Control. This is a global setting. |

|         |       | 0000 = COLX                             |

|         |       | 0001 = ERROR                            |

|         |       | 0010 = DUPLEX                           |

|         |       | 0011 = DUPLEX/COLX                      |

|         |       | 0100 = SPEED                            |

|         |       | 0101 = LINK                             |

|         |       | 0110 = TX                               |

|         |       | 0111 = RX                               |

|         |       | 1000 = ACT                              |

|         |       | 1001 = LINK/RX                          |

|         |       | 1010 = LINK/ACT                         |

|         |       | 1011 = ACT (Blink mode)                 |

|         |       | 1100 = TX (Blink Mode)                  |

|         |       | 1101 = RX (Blink Mode)                  |

|         |       | 1110 = Interrupt                        |

|         |       | 1111 = Force off                        |

Table 21: PHY LED Control (Continued)

| Bits   | Field | Description                             |

|--------|-------|-----------------------------------------|

| 22.7:4 | LED1  | LED1 Control. This is a global setting. |

|        |       | 0000 = COLX                             |

|        |       | 0001 = ERROR                            |

|        |       | 0010 = DUPLEX                           |

|        |       | 0011 = DUPLEX/COLX                      |

|        |       | 0100 = SPEED                            |

|        |       | 0101 = LINK                             |

|        |       | 0110 = TX                               |

|        |       | 0111 = RX                               |

|        |       | 1000 = ACT                              |

|        |       | 1001 = LINK/RX                          |

|        |       | 1010 = LINK/ACT                         |

|        |       | 1011 = ACT (Blink mode)                 |

|        |       | 1100 = TX (Blink Mode)                  |

|        |       | 1101 = RX (Blink Mode)                  |

|        |       | 1110 = COLX (Blink Mode)                |

|        |       | 1111 = Force off                        |

Table 21: PHY LED Control (Continued)

| Bits   | Field | Description                             |

|--------|-------|-----------------------------------------|

| 22.3:0 | LED0  | LED0 Control. This is a global setting. |

|        |       | 0000 = COLX                             |

|        |       | 0001 = ERROR                            |

|        |       | 0010 = DUPLEX                           |

|        |       | 0011 = DUPLEX/COLX                      |

|        |       | 0100 = SPEED                            |

|        |       | 0101 = LINK                             |

|        |       | 0110 = TX                               |

|        |       | 0111 = RX                               |

|        |       | 1010 = LINK/ACT                         |

|        |       | 1011 = ACT (Blink mode)                 |

|        |       | 1100 = TX (Blink Mode)                  |

|        |       | 1101 = RX (Blink Mode)                  |

|        |       | 1110 = COLX (Blink Mode)                |

|        |       | 1111 = Force off                        |

Table 22: Speed Dependent Behavior

| Bits   | Field      | Description                                                                                                                                                                      |

|--------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24.8:6 | LED2 Speed | LED 2 Speed Select 000 = Active for 10BASE-T Link 001 = Reserved 010 = Reserved 011 = Reserved 100 = Reserved 100 = Reserved 101 = Active for 100BASE-X 110 = Off 111 = Reserved |

| 24.5:3 | LED1 Speed | LED 1 Speed Select  000 = Active for 10BASE-T Link  001 = Reserved  010 = Reserved  011 = Reserved  100 = Reserved  101 = Active for 100BASE-X  110 = Off  111 = Reserved        |

| 24.2:0 | LED0 Speed | LED 0 Speed Select  000 = Active for 10BASE-T Link  001 = Reserved  010 = Reserved  011 = Reserved  100 = Reserved  101 = Active for 100BASE-X  110 = Off  111 = Reserved        |

## 2.11.3 LED Polarity

The polarity of the LED in the active state can be set through register 25.14:12.

Table 23: LED Active Polarity

| Bits  | Field   | Description                                                                                                 |  |

|-------|---------|-------------------------------------------------------------------------------------------------------------|--|

| 25.14 | InvLED2 | Invert LED2. This bit controls the active level of the LED2 pin.  0 = Active Low LED2  1 = Active High LED2 |  |

| 25.13 | InvLED1 | Invert LED1. This bit controls the active level of the LED1 pin.  0 = Active Low LED1  1 = Active High LED1 |  |

| 25.12 | InvLED0 | Invert LED0. This bit controls the active level of the LED0 pin.  0 = Active Low LED0  1 = Active High LED0 |  |

## 2.11.4 Stretching and Blinking

Some of the statuses can be pulse stretched. Pulse stretching is necessary because the duration of these status events might be too short to be observable on the LEDs. The pulse stretch duration can be programmed via Register 24.14:12. The default pulse stretch duration is set to 170 to 340 ms. The pulse stretch duration applies to all applicable LEDs.

Some of the statuses indicate multiple events by blinking LEDs. The blink period can be programmed via Register 24.11:9. The default blink period is set to 84 ms. The blink rate applies to all applicable LEDs.

## 2.12 Automatic and Manual Impedance Calibration

#### 2.12.1 MAC Interface Calibration Circuit

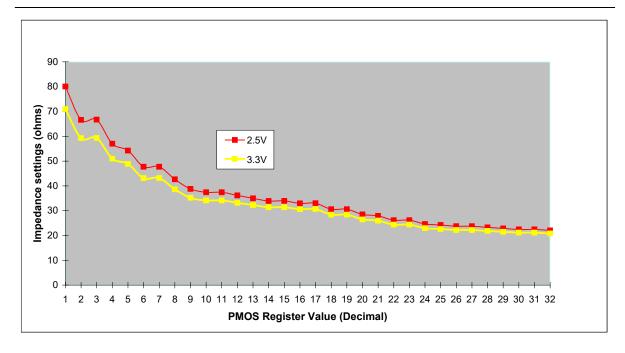

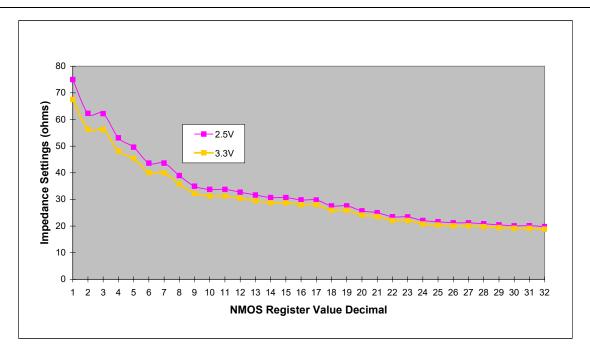

The auto calibration is available for the MAC interface I/Os. The PHY runs the automatic calibration circuit with a 49 ohm impedance target by default after hardware reset. Other impedance targets are available by changing the impedance target and restarting the auto calibration through register writes. Individual NMOS and PMOS output transistors could be controlled for 38 to 80 ohm targets in various increments.

Manual NMOS and PMOS settings are available if the automatic calibration is not desired. If the PCB traces are different from 50 ohms, the output impedance of the MAC interface I/O buffers can be programmed to match the trace impedance. Users can adjust the NMOS and PMOS driver output strengths to perfectly match the transmission line impedance and eliminate reflections completely.

## 2.12.2 MAC Interface Calibration Register Definitions

If Register 29 = 0x000A, then Register 30 is defined as follows:

Table 24: Register 30 Page 10 - MAC Interface Calibration Definitions

| Reg<br>bit | Function            | Setting description                                                                                           | Mode | HW<br>Reset          | SW<br>Reset |  |

|------------|---------------------|---------------------------------------------------------------------------------------------------------------|------|----------------------|-------------|--|

| 15         | Restart Calibration | 0 = Normal                                                                                                    | R/W  | 0                    | Retain      |  |

|            |                     | 1 = Restart                                                                                                   |      |                      |             |  |

|            |                     | Bit 15 is a self-clearing register. Calibration will start once the register is cleared.                      |      |                      |             |  |

| 14         | Calibration Com-    | 1 = Calibration complete                                                                                      | RO   | 0                    | Retain      |  |

|            | plete               | 0 = Calibration in progress                                                                                   |      |                      |             |  |

| 13         | Reserved            | 0                                                                                                             | R/W  | 0                    | Retain      |  |

| 12:8       | PMOS Value          | 00000 = All fingers off                                                                                       | R/W  | Auto cal-<br>ibrated | Retain      |  |

|            |                     | 11111 = All fingers on                                                                                        |      | value                |             |  |

|            |                     | The automatic calibrated values are stored here after calibration completes.                                  |      |                      |             |  |

|            |                     | Once the LATCH bit is set to 1, the new calibration value is written. The automatic calibrated value is lost. |      |                      |             |  |

| 7          | Reserved            | 0                                                                                                             | R/W  | 0                    | Retain      |  |

| 6          | Latch               | 1 = Latch in new value. This bit self clears.                                                                 | R/W, | 0                    | Retain      |  |

|            |                     | (Used for manual settings)                                                                                    | SC   |                      |             |  |

Table 24: Register 30 Page 10 - MAC Interface Calibration Definitions (Continued)

| Reg<br>bit | Function         | Setting description                                                                                           | Mode | HW<br>Reset                   | SW<br>Reset |